7740DLY-AES4 Four Channel AES Delay

| 1. | OVERVIEW                                                                         | 1  |

|----|----------------------------------------------------------------------------------|----|

| 2. | INSTALLATION                                                                     | 2  |

|    | 2.1. REFERENCE INPUT                                                             | 2  |

|    | 2.2. AES DIGITAL AUDIO INPUTS AND OUTPUTS                                        | 2  |

| 3. | SPECIFICATIONS                                                                   | 3  |

|    | 3.1. VIDEO REFERENCE                                                             |    |

|    | 3.2. AES DIGITAL AUDIO REFERENCE                                                 | 3  |

|    | 3.3. AES AUDIO INPUTS                                                            | 4  |

|    | 3.4. AES AUDIO OUTPUTS                                                           | 4  |

|    | 3.5. DELAY RESOLUTION AND RANGE                                                  | 4  |

|    | 3.6. ELECTRICAL                                                                  | 4  |

|    | 3.7. PHYSICAL                                                                    | 4  |

| 4. | STATUS LEDS                                                                      | 5  |

|    | 4.1. MODULE STATUS LEDS                                                          | 5  |

|    | 4.2. AES I/O STATUS LEDS                                                         | 5  |

| 5. | CARD EDGE CONTROLS                                                               | 6  |

|    | 5.1. SELECTING SAMPLE RATE CONVERSION ON THE AES INPUTS                          | 6  |

|    | 5.2. SELECTING 20 OR 24-BIT OPERATION                                            | 6  |

|    | 5.3. SELECTING CHANNEL SWAP OPERATION                                            | 6  |

| 6. | DELAY ADJUSTMENT                                                                 | 7  |

|    | 6.1. ADJUSTING FINE DELAY                                                        | 8  |

|    | 6.2. ADJUSTING COARSE DELAY                                                      | 8  |

| 7. | JUMPERS AND USER ADJUSTMENTS                                                     | 9  |

|    | 7.1. SELECTING WHETHER LOCAL FAULTS WILL BE MONITORED BY THE GLOBAL FRAME STATUS | 9  |

|    | 7.2. CONFIGURING THE MODULE FOR FIRMWARE UPGRADES                                | 9  |

|    | 7.3. SELECTING WHETHER THE GENLOCK REFERENCE INPUT IS TERMINATED                 | 10 |

# 7700 MultiFrame Manual 7740DLY-AES4 Four Channel AES Delay

| Figures                                                     |   |

|-------------------------------------------------------------|---|

| Figure 1: 7740DLY-AES4 Block Diagram                        | 1 |

| Figure 2: 7740DLY-AES4 Rear Panel                           | 2 |

| Figure 3: Location of Jumpers on 7740DLY-AES4               | g |

| Tables                                                      |   |

| Table 1: Pinout of AES I/O Connector                        |   |

| Table 2: Delay Resolution and Range                         | 4 |

| Table 3: Audio Status LEDs                                  | 5 |

| Table 4: Main DIP Switch Functions                          | 6 |

| Table 5: Sample Rate Conversion Switch Settings             | 6 |

| Table 6: Audio Sample Resolution Switch Settings            | 6 |

| Table 7: Channel Swap Switch Settings                       | 7 |

| Table 8: Delay Selection in Fine Mode                       | 8 |

| Table 9: Delay Selection in Coarse Mode with NTSC Reference | 8 |

| Table 10: Delay Selection in Coarse Mode with PAL Reference |   |

# **REVISION HISTORY**

| <u>REVISION</u> |                        | <u>DESCRIPTION</u> | DATE    |

|-----------------|------------------------|--------------------|---------|

| 0.1             | Preliminary Version    |                    | Mar 01  |

| 1.0             | First official release |                    | July 01 |

This page left intentionally blank

## 1. OVERVIEW

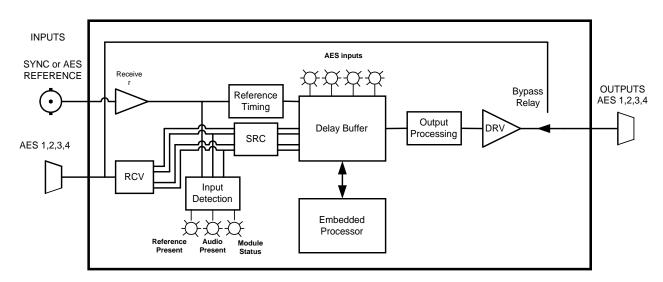

The 7740DLY-AES4 quad AES digital audio delay provides independent fine or coarse delay for AES digital inputs. The module accepts either an analog composite sync or AES digital audio reference and a maximum of four asynchronous / synchronous 48KHz single ended AES inputs or eight audio channels. Each AES pair can be sample rate converted along with independent channel swap operation. External loop-through connections can be applied for cascaded delays to achieve two, three or four times of maximum delay as specified for one AES signal.

#### Features:

- Automatically detect and lock to either external analog composite sync or AES digital audio reference

- Process delay for four asynchronous / synchronous 48KHz single ended AES digital audio inputs simultaneously

- Independent control for each AES input pair (AES input 1 and 2, 3 and 4)

- Support audio sample resolutions of 20 and 24 bits

- Selectable sample rate conversion or passthrough input audio processing

- Support audio channel swap operation for all AES inputs simultaneously

- Selectable fine or coarse delay in 1.04ms (50 samples) or video field, respectively

- Maximum delay of 2.13sec and 2.56sec for NTSC and PAL mode, respectively

- Bypass relay outputs at the loss of power

- Card edge LEDs indicate reference presence, audio input presence and swap mode operation.

Figure 1: 7740DLY-AES4 Block Diagram

## 2. INSTALLATION

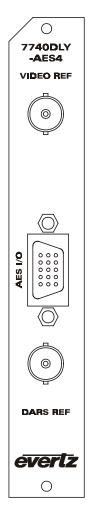

The 7740DLY-AES4 modules each come with a companion rear plate that has two BNCs and a female high-density DB15 connector. For information on mounting the rear plate and inserting the module into the frame see section 3 of the 7700FR chapter.

Figure 2: 7740DLY-AES4 Rear Panel

#### 2.1. REFERENCE INPUT

In order to properly delay the AES audio, the 7740DLY-AES4 must be references to a video or digital audio source. The 7740DLY-AES4 automatically detects which type of reference is supplied.

VIDEO REF For a video reference connect an NTSC or PAL colour black or composite sync signal

**DARS REF** For a digital audio reference connect a 48KHz single ended AES signal compatible with SMPTE 276M.

## 2.2. AES DIGITAL AUDIO INPUTS AND OUTPUTS

The AES digital audio inputs consists of four asynchronous / synchronous 48KHz single ended AES signals; and AES outputs are delayed version of the associated inputs. All AES outputs are protected by

bypass relays that activates in the event of power loss to the module. All AES digital audio signals are compatible with SMPTE 276M.

The following is the pinout of the female HD DB15 connector labeled AES I/O

| DB15  | Name      | Description    |  |  |  |  |

|-------|-----------|----------------|--|--|--|--|

| 1     | NC        | Not connected  |  |  |  |  |

| 2     | NC        | Not connected  |  |  |  |  |

| 3     | NC        | Not connected  |  |  |  |  |

| 4     | NC        | Not connected  |  |  |  |  |

| 5     | NC        | Not connected  |  |  |  |  |

| 6     | NC        | Not connected  |  |  |  |  |

| 7     | AES IN 1  | Audio input 1  |  |  |  |  |

| 8     | NC        | Not connected  |  |  |  |  |

| 9     | AES OUT 2 | Audio output 2 |  |  |  |  |

| 10    | AES OUT 1 | Audio output 1 |  |  |  |  |

| 11    | AES IN 2  | Audio input 2  |  |  |  |  |

| 12    | AES OUT 4 | Audio output 4 |  |  |  |  |

| 13    | AES OUT 3 | Audio output 3 |  |  |  |  |

| 14    | AES IN 4  | Audio input 4  |  |  |  |  |

| 15    | AES IN 3  | Audio input 3  |  |  |  |  |

| Shell | GND       | Ground         |  |  |  |  |

Table 1: Pinout of AES I/O Connector

## 3. SPECIFICATIONS

## 3.1. VIDEO REFERENCE

Type: NTSC or PAL Colour Black nominal 1 V p-p

Composite Bi-level sync (525I or 625I) 300 mV

**Connector:** 1 BNC per IEC 169-8

**Termination:** 75 ohm (jumper selectable)

### 3.2. AES DIGITAL AUDIO REFERENCE

**Standard:** SMPTE 276M, single ended asynchronous or synchronous AES audio

**Connector:** BNC per IEC 169-8

**Resolution:** 20 or 24 bits

Sampling Rate: 48 KHz

**Impedance:** 75 Ohms unbalanced

#### 3.3. AES AUDIO INPUTS

Number of Inputs: 4

**Standard:** SMPTE 276M, single ended asynchronous or synchronous AES audio

**Connectors:** 15 pin High density D

**Resolution:** 20 or 24 bits **Sampling Rate:** 48 KHz

**Impedance:** 75 Ohms unbalanced

#### 3.4. AES AUDIO OUTPUTS

Number of Outputs: 4

**Standard:** SMPTE 276M, single ended asynchronous or synchronous AES audio

**Connectors:** 15 pin High density D

**Resolution:** 20 or 24 bits **Sampling Rate:** 48 KHz

**Impedance:** 75 Ohms unbalanced

## 3.5. DELAY RESOLUTION AND RANGE

The 7740DLY-AES4 provides either fine or coarse delay selection for each AES input pair.

| Delay mode | Resolution          | Maximum delay    |  |

|------------|---------------------|------------------|--|

| Fine       | 1.04ms (50 samples) | 132.08ms         |  |

| Coarse     | 1 video field       | 127 video fields |  |

**Table 2: Delay Resolution and Range**

Note: minimum delay for either fine or coarse delay mode is about one video line, i.e.  $63.5\mu s$  for NTSC or  $64\mu s$  for PAL.

#### 3.6. ELECTRICAL

**Voltage:** + 12VDC **Power:** 6 Watts.

**EMI/RFI:** Complies with FCC Part 15, class A and EU EMC directive.

## 3.7. PHYSICAL

#### 7700 or 7701 frame mounting:

Number of slots: 1

**Stand Alone Enclosure:**

**Dimensions:** 14 " L x 4.5 " W x 1.9 " H

(355 mm L x 114 mm W x 48 mm H)

Weight: approx. 1.5 lbs. (0.7 Kg)

## 4. STATUS LEDS

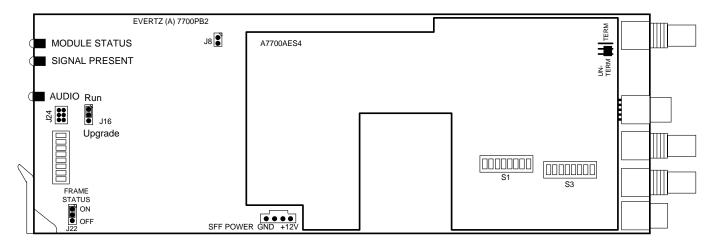

The location of the status LEDs is shown in Figure 3.

## 4.1. MODULE STATUS LEDS

MODULE OK This Green LED will be ON when the module is operating properly

LOCAL FAULT This Red LED makes it easy to identify one module in a frame that is missing an

essential input or has another fault.

The LED will blink ON and OFF if the microprocessor is not running.

The LED will be ON solid when input video is missing, or audio is missing from both

AES inputs or there is a fault in the module power supply.

SIGNAL PRESENT This Green LED will be ON when there is a valid analog composite sync or AES

audio reference present at the module input.

AUDIO This Green LED will be ON solid when there are valid AES audio signals present on

all four AES inputs.

The LED will blink ON and OFF when there are valid AES audio signals present on

at least one of the AES inputs.

#### 4.2. AES I/O STATUS LEDS

Four LEDs located on the lower end of the module (opposite the DIP switch) indicate the status of the audio input and associated operation. Status LED 1 is located closest to the center of the module.

| AES                                         | Color                                                       | Status                                                                      |

|---------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------|

| LED                                         |                                                             |                                                                             |

| 1                                           | Off                                                         | There is no valid AES input 1 present                                       |

|                                             | On                                                          | AES input 1 is being delayed, and presented as AES output 1                 |

|                                             | Flashing                                                    | AES input 1 is being delayed, channel swapped and presented as AES output 1 |

| 2                                           | Off                                                         | There is no valid AES input 2 present                                       |

|                                             | On                                                          | AES input 2 is being delayed, and presented as AES output 2                 |

|                                             | Flashing                                                    | AES input 2 is being delayed, channel swapped and presented as AES output 2 |

| 3 Off There is no valid AES input 3 present |                                                             | There is no valid AES input 3 present                                       |

|                                             | AES input 3 is being delayed, and presented as AES output 3 |                                                                             |

|                                             | Flashing                                                    | AES input 3 is being delayed, channel swapped and presented as AES output 3 |

| 4                                           | Off                                                         | There is no valid AES input 4 present                                       |

|                                             | On                                                          | AES input 4 is being delayed, and presented as AES output 4                 |

|                                             | Flashing                                                    | AES input 4 is being delayed, channel swapped and presented as AES output 4 |

**Table 3: Audio Status LEDs**

## 5. CARD EDGE CONTROLS

The 7740DLY-AES4 is equipped with an 8 position DIP switch at the front of the card to allow the user to select various functions. All positions are assigned sequentially such that the first position is located at the top of the DIP switch (farthest from to the card ejector). Sections 5.1 to 5.3 show the assigned DIP switch functions. The ON position is down, or closest to the printed circuit board. Table 4 gives an overview of the DIP switch functions. There are also 2 DIP switches located on the 7700-AES4 submodule. These switches are used to set the delay time. Section 6 describes how to set the video delay for the module.

| DIP Switch | Function                                           |  |  |  |

|------------|----------------------------------------------------|--|--|--|

| 1          | Sample rate conversion (SRC) for AES input 1 and 2 |  |  |  |

| 2          | 20/24-bit selection for AES input 1 and 2          |  |  |  |

| 3          | Sample rate conversion (SRC) for AES input 3 and 4 |  |  |  |

| 4          | 20/24-bit selection for AES input 3 and 4          |  |  |  |

| 5          | Channel swap for AES input 1                       |  |  |  |

| 6          | Channel swap for AES input 2                       |  |  |  |

| 7          | Channel swap for AES input 3                       |  |  |  |

| 8          | Channel swap for AES input 4                       |  |  |  |

**Table 4: Main DIP Switch Functions**

## 5.1. SELECTING SAMPLE RATE CONVERSION ON THE AES INPUTS

The AES receivers in the 7740DLY-AES4 can perform input audio processing in either pass-through or sample rate conversion mode. DIP switch 1 (input 1 and 2) and 3 (input 3 and 4) are used to enable sample rate conversion for the AES inputs.

| DIP 1 or 3 | SRC Enable   |  |  |

|------------|--------------|--|--|

| OFF        | Pass-through |  |  |

| ON         | SRC          |  |  |

**Table 5: Sample Rate Conversion Switch Settings**

#### 5.2. SELECTING 20 or 24-BIT OPERATION

DIP switch 2 (input 1 and 2) and 4 (input 3 and 4) are used to select whether the AES input has 20 or 24 bit audio samples.

| DIP 2 or 4 | Audio Sample Resolution |  |  |

|------------|-------------------------|--|--|

| OFF        | 24 bits                 |  |  |

| ON         | 20 bits                 |  |  |

Table 6: Audio Sample Resolution Switch Settings

## 5.3. SELECTING CHANNEL SWAP OPERATION

DIP switches 5 to 8 are used to select the channel swap operation for AES inputs 1 to 4, respectively. When the switch is Off, the associated AES channel pair will be delayed by the amount selected with the delay DIP switches. When the switch is ON, the left and right channels of the pair will be swapped after the delay is added.

| DIP 5, 6, 7, 8 | Channel Swap Enable     |  |  |

|----------------|-------------------------|--|--|

| Off            | Delay only              |  |  |

| On             | Delay with channel swap |  |  |

**Table 7: Channel Swap Switch Settings**

## 6. DELAY ADJUSTMENT

The 7740DLY-AES4 is equipped with two 8-position DIP switches (located on the A7700-AES4 sub-board) to allow the user to adjust the delay that will be applied to the AES audio. Each DIP switch is used to set the delay for two AES channels and is measured with respect to the input reference. Table 8 gives an overview of the DIP switch functions. For simplicity the manual will discuss setting the delay for AES inputs 1 and 2 using DIP switch S1. Setting the delay for AES inputs 3 and 4 is identical but uses DIP switch S3.

| Switch | Function                    |  |  |

|--------|-----------------------------|--|--|

| 1      | Fine / coarse selection     |  |  |

|        | ON - fine delay mode        |  |  |

|        | OFF- coarse delay mode      |  |  |

| 2 to 8 | 128 selectable delay values |  |  |

|        | MSB is pin 2, LSB is pin 8  |  |  |

**Table 8: Delay DIP Switch Functions**

Minimum delay is achieved by setting switches 2 to 8 to "OFF" position. When all are "ON" position, maximum delay is set.

## 6.1. ADJUSTING FINE DELAY

Delay switch is set to fine mode when switch #1 is ON. Switches 2 to 8 are used as a binary number to set one of 128 possible delay values. The minimum delay when all switches are off and the Sample Rate converter is off is 145  $\mu$ sec. When the Sample Rate Converter for the AES input is turned On there is an additional delay of 1.8 msec. The incremental delay value between each switch selection is 50 audio samples or approximately 1.04msec. Details are illustrated in Table 8.

| Switch |     |     |     |     | Sample Rate Converter |     |            |           |

|--------|-----|-----|-----|-----|-----------------------|-----|------------|-----------|

| 2      | 3   | 4   | 5   | 6   | 7                     | 8   | Off        | On        |

| Off    | Off | Off | Off | Off | Off                   | Off | 145us      | 1.92msec  |

| Off    | Off | Off | Off | Off | Off                   | On  | 1.18msec   | 2.96msec  |

| Off    | Off | Off | Off | Off | On                    | Off | 2.22msec   | 4.00msec  |

|        |     |     |     |     |                       |     |            |           |

| On     | On  | On  | On  | On  | On                    | Off | 131.36msec | 131.6msec |

| On     | On  | On  | On  | On  | On                    | On  | 132.4msec  | 134.2msec |

**Table 8: Delay Selection in Fine Mode**

## 6.2. ADJUSTING COARSE DELAY

Delay switch is set to fine mode when switch #1 is OFF. Switches 2 to 8 are used as a binary number to set one of 128 possible coarse delay values. The incremental delay value between each switch selection is exactly 1 video field for either NTSC (16.68msec) or PAL (20.0msec) reference. Details are illustrated in Table 9 and Table 10.

|     |     | 5   | Switc | h   |     |     | Delay  |           |           |  |

|-----|-----|-----|-------|-----|-----|-----|--------|-----------|-----------|--|

| 2   | 3   | 4   | 5     | 6   | 7   | 8   | Fields | SRC Off   | SRC On    |  |

| Off | Off | Off | Off   | Off | Off | Off | 0      | 210μs     | 1.95msec  |  |

| Off | Off | Off | Off   | Off | Off | On  | 1      | 16.89msec | 18.63msec |  |

| Off | Off | Off | Off   | Off | On  | Off | 2      | 33.57msec | 35.31msec |  |

|     |     |     |       |     |     |     |        |           |           |  |

| On  | On  | On  | On    | On  | On  | Off | 126    | 2.10sec   | 2.10sec   |  |

| On  | On  | On  | On    | On  | On  | On  | 127    | 2.12sec   | 2.12sec   |  |

Table 9: Delay Selection in Coarse Mode with NTSC Reference

|     |     | 5   | Switc | h   |     |     | Delay  |          |           |

|-----|-----|-----|-------|-----|-----|-----|--------|----------|-----------|

| 2   | 3   | 4   | 5     | 6   | 7   | 8   | Fields | SRC Off  | SRC On    |

| Off | Off | Off | Off   | Off | Off | Off | 0      | 210μs    | 1.95msec  |

| Off | Off | Off | Off   | Off | Off | On  | 1      | 20.2msec | 21.95msec |

| Off | Off | Off | Off   | Off | On  | Off | 2      | 40.2msec | 41.95msec |

|     |     |     |       |     |     |     |        |          |           |

| On  | On  | On  | On    | On  | On  | Off | 126    | 2.50sec  | 2.50sec   |

| On  | On  | On  | On    | On  | On  | On  | 127    | 2.54sec  | 2.54sec   |

Table 10: Delay Selection in Coarse Mode with PAL Reference

## 7. JUMPERS AND USER ADJUSTMENTS

Figure 3: Location of Jumpers on 7740DLY-AES4

# 7.1. SELECTING WHETHER LOCAL FAULTS WILL BE MONITORED BY THE GLOBAL FRAME STATUS

#### FRAME STATUS

The FRAME STATUS jumper located at the front of the module determines whether local faults (as shown by the Local Fault indicator) will be connected to the 7700FR frame's global status bus.

To monitor faults on this module with the frame status indicators (on the PS FRAME STATUS LED's and on the Frame's Fault Tally output) install this jumper in the On position. (Default)

When this jumper is installed in the Off position, local faults on this module will not be monitored.

#### 7.2. CONFIGURING THE MODULE FOR FIRMWARE UPGRADES

#### **UPGRADE**

The UPGRADE jumper J16 located at the front of the module is used when firmware upgrades are being done to the module. For normal operation it should be installed in the *RUN* position. See the *Upgrading Firmware* section of this manual for more information.

To upgrade the firmware in the module unit pull it out of the frame. Move Jumper J16 into the *UPGRADE* position. Install the Upgrade cable provided (located in the vinyl pouch in the front of this manual) onto header J24 at the card edge. Re-install the module into the frame. Run the upgrade as described in the *Upgrading Firmware* section of this manual. Once the upgrade is completed, remove the module from the frame, move J16 into the *RUN* position, remove the upgrade cable and re-install the module. The module is now ready for normal operation.

# 7.3. SELECTING WHETHER THE GENLOCK REFERENCE INPUT IS TERMINATED

## **TERM/UNTERM**

The TERM/UNTERM jumper J2 located on the A7700-AES4 Audio submodule is used to terminate the genlock input. When it is in the TERM position a 75 ohm terminating resistor will be connect the input to ground. When it is in the UNTERM position the genlock input will be high impedance.